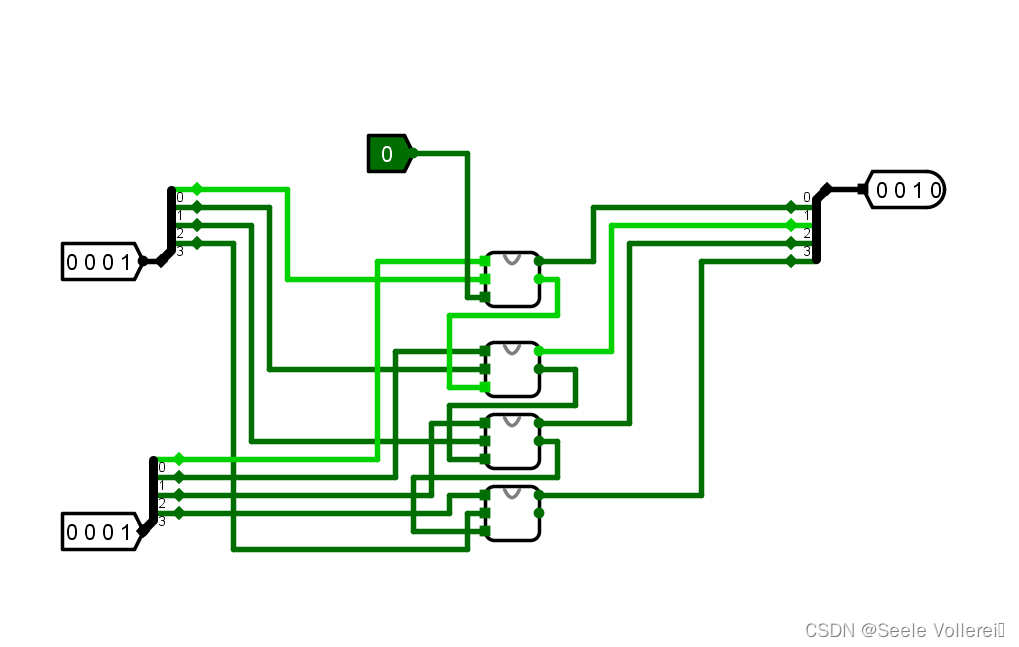

印象中always块内被赋值verilogregwire区别的只能是reg型信号虽然在电平敏感情况下综合出来的器件大都不是触发器这是verilog的一种语法规则,物理的触发器和程序中的reg有一定区别reg型信号可以在程序中的任何地方被引用,不限于always块内;Verilog中的数组和存储器可以概括如下数组 定义在Verilog中,数组是用于存储一系列数据的结构,可以是标量或向量,支持多维数组 数据类型数组可以使用regwireintegerreal四种数据类型进行声明 访问方式访问数组元素时需要指定每个维度的索引 示例 一个8bit向量mem1 深度为4的。

这是一个历史遗留问题在 Verilog 被 Cadence 买下之前大约上世纪八九十年代的样子,Verilog 只是一个用来做仿真的 HDL,不可综合在那个年代,仿真器看到 wire 和 reg 会区别处理实际上至今也是这样不知道你有没有发现,reg 类型信号的跳变,是依靠输入和敏感列表的,而且在非阻塞赋值中;Verilog总结层次结构Verilog的描述层次包括行为级RTL级和门级,每层有其特定的职责和应用场景基础代码与数据类型基础代码示例如二进制与门模块展示verilogregwire区别了Verilog的基本结构数据类型包括整数实数字符串以及标识符reg和wire是两种基本的数据类型,分别用于存储和驱动信号integer和time用于时间相关。

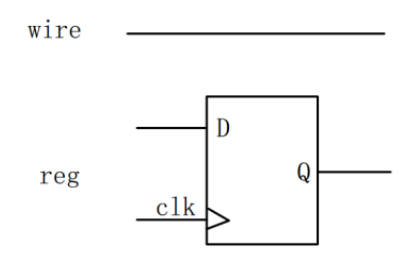

reg即寄存器类型,会占用资源wire即线网类型,不占用资源你可以理解为reg就是一个小的存储体,而wire就是连接线。

verilog中reg和wire类型的区别和用法

1、Verilog与CJava等计算机编程语言有本质的不同在Verilog中,几乎所有写出的内容都会对应到实际的电路中例如,声明一个reg类型的变量时,这个变量就具有寄存数值的功能,并可以综合成一个实际的寄存器声明一个wire类型的变量时,它只能用于传递数据,仅表示一条线代码与电路的对应关系在Verilog中。

2、reg是寄存器,特点是输出只在时钟边沿时变化所以必须在always语句内才能赋值wire类型是组合逻辑,类似于一些与非异或门电路,可以在任何地方改变赋值,包括always块内。

3、从名字上来看,wire意味着连线,实际上在电路中,它扮演的角色就像一根导线,用于连接电路中的各个部分而reg则代表寄存器,它在电路中起到寄存数据的作用连线和寄存器构成verilogregwire区别了数字电路的基础结构,这也是verilog这两种变量类型的基本来源在verilog的后续版本systemverilog中,引入了更多更为抽象化的变量类型。

4、reg相当于存储单元,wire相当于物理连线 Verilog 中变量的物理数据分为线型和寄存器型这两种类型的变量在定义时要设置位宽,缺省为1位变量的每一位可以是0,1,X,Z其中x代表一个未被预置初始状态的变量或者是由于由两个或多个驱动装置试图将之设定为不同的值而引起的冲突型线型变量z代表高阻。

5、两者的区别是寄存器型数据保持最后一次的赋值,而线型数据需要持续的驱动wire使用在连续赋值语句中,而reg使用在过程赋值语句initial ,always中wire若无驱动器连接,其值为z,reg默认初始值为不定值 x 在连续赋值语句中,表达式右侧的计算结果可以立即更新表达式的左侧在理解上,相当于一个。

6、在Verilog编程中,reg和wire这两个概念常常引起初学者的疑惑简单来说,reg和wire的主要区别在于它们在always块中的使用以及编译后的电路实现官方定义中,reg可以理解为存储单元,它具有记忆功能,能保持上次的输入值,无需持续激励相比之下,wire更像是物理连线,它需要通过assign指令来赋值,不能在al。

7、首先要先清楚一点,verilog是硬件描述语言,其最终是为了生成一个电路,所以它的变量类型是根据实际电路来决定的从名字理解wire,线型,实际上在电路中的作用就是一根连线reg,寄存器型,在电路中就作为寄存器存在连线和寄存器是构成数字电路的基本结构,这也是verilog这两种变量类型的来源当然,在。

veriloga和verilog的区别

1、尽管两种语言在实现细节上有区别,但它们都致力于描述硬件的行为因此,在设计硬件电路时,可以根据具体需求选择合适的语言进行编写Verilog和VHDL都是硬件描述语言HDL,用于描述数字电路的行为其中,reg类型主要用于存储数据,而wire类型用于表示信号的连接在Verilog中,通过将一个reg类型的信号赋值为。

2、在学习Verilog语法的过程中,小白认识到reg和wire在编程中的重要区别这两者在数字电路设计中扮演着传输与存储的角色,就像信号的流动与存储单元wire通常用于组合逻辑电路,可以作为输入接收表达式的输出,或通过assign赋值其声明格式为wire n10 signal_name相比之下,reg型变量则更像触发器,适。

3、reg always语句,满足时序逻辑时,给reg型赋值verilogregwire区别他代表是一个寄存器比如always @negedge clka1lt=a2wireassign语句或者直接wire c1lt=c2表示连续赋值,赋值右边变化即刻通过“连线”传递到左边这个语句在通电就有效。

4、在Verilog中,数组和存储器是关键组件,用于数据存储与处理数组声明可包括标量和向量,多维数组可通过指定地址范围创建Verilog允许使用reg,wire,integer,real四种数据类型进行数组声明访问数组元素需指定每个维度的索引不同数据类型可在Verilog中构建数组,但n个1bit的reg与n位向量在存储上有所区别。

5、#8226 无敏感列表,描述组合逻辑,和assign语句是有区别的 assign赋值语句和always@*语句之间的差别有1被assign赋值的信号定义为wire型,被always@*结构块下的信号定义为reg型,值得注意的是,这里的reg并不是一个真正的触发器,只有敏感列表为上升沿触发的写法才会综合为触发器,在仿真时才。

还没有评论,来说两句吧...